本文作者:柏嘉玮,Cadence 公司 DSG Product Engineering Group

Integrity 3D-IC 平台

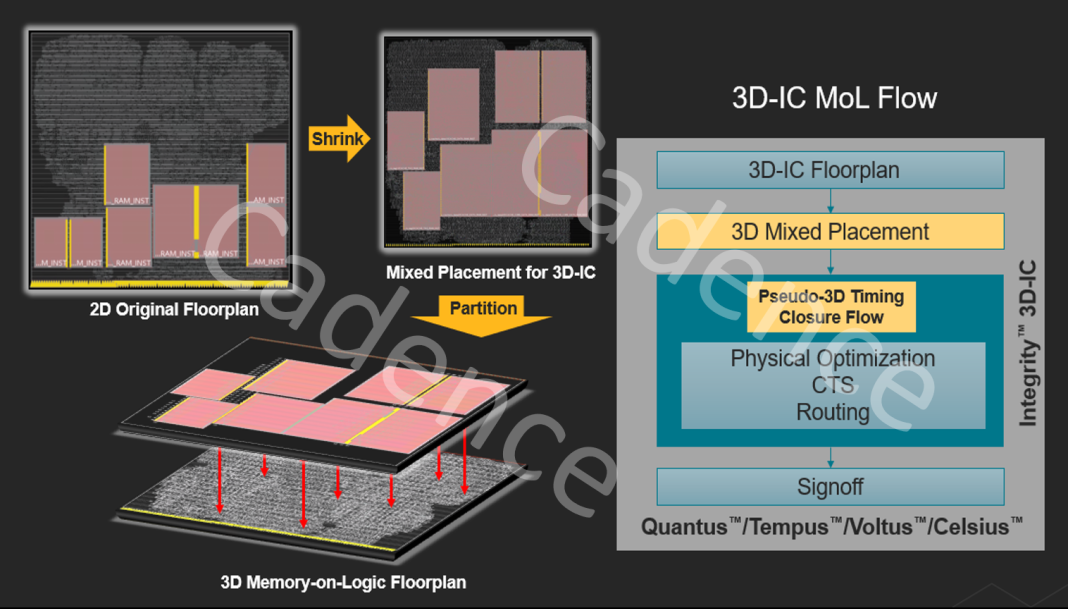

提供了一系列三维堆叠设计流程,通过将二维芯片网表分解成双层的三维堆叠结构,用户可以探索三维堆叠裸片系统相对于传统二维设计的性能优势,改善内存延迟,实现性能突破。

从二维设计中分离出存储单元,并自动将其划分为两个工艺层,上层放置存储单元 Macro Cells,下层放置逻辑运算单元 Standard Cells。该流程可以实现两个裸片同时进行的时序驱动单元摆放。用户还可以进一步运行标准的实现步骤,如时钟树综合、时序优化、布线等,将其作为传统布局布线流程来完成三维堆叠设计实现。

今天我们来介绍 Integrity 3D-IC 的特色功能之一:

Memory-on-Logic 三维芯片堆叠设计流程

What is Memory-on-Logic?

Memory 指的是记忆存储单元;Logic 指的是运算单元或处理单元。

Memory-on-logic(MoL)堆叠顾名思义,就是将存储单元通过三维堆叠的设计方式,放置在运算单元所在裸片的上层裸片中,从而实现三维集成电路的三维堆叠结构。

Why is Memory-on-Logic?

我们现在正处于高速发展的人工智能时代,对计算机算力的需求日益旺盛,同时也对相关的集成电路芯片提出了更高的性能要求。

然而算力需求的快速增长和有限的算力提升速度形成了尖锐的矛盾,其具体表现在两个方面:一是如今的摩尔定律越来越难以维系,器件尺寸微缩越来越困难;二个是现有的计算机架构——冯诺依曼存算分离架构的缺陷开始凸显,出现了所谓的内存墙限制(Memory Wall Limitation)。

MoL 三维堆叠结构为上述瓶颈提供了解决思路。对于后摩尔时代背景下的工艺瓶颈,三维堆叠可以有效提升单位投影面积中晶体管的数目,3D-IC 从方法学角度提供了一种延续摩尔定律的可能;对于存算分离所引起的内存墙限制,通过把存储单元通过三维堆叠放置到逻辑运算单元的正上方,尽可能缩短数据传输距离,从而进一步提升芯片性能,降低数据传输的功耗。此外,通过 3D-IC Memory-on-Logic 结构还可以对上下裸片采用不同的工艺制程,从而降低整体芯片的制造成本。

How to do Memory-on-Logic?

后端实现流程如下图所示,对比传统二维芯片,三维 MoL 芯片基于 3D-IC 专用物理后端实现平台——Integrity 3D-IC,从 floorplan 阶段开始就加入 3D-IC 的设计方法,通过 3D Mixed Placer 引擎同时进行 Macro Cells 和 Standard Cells 的自动布局,建立 Pseudo-3D 时序收敛流程,从而实现 3D-IC MoL 的迭代优化、时钟树综合、自动绕线等步骤,在签核阶段还可以通过 Integrity 3D-IC 平台来调用各类 Signoff 工具实现各项签核。

1. 3D Mixed Placement

规划 Floorplan 是传统数字后端实现流程早期的一个重要阶段,主要目标之一便是 Macro Cells 的放置。传统 Floorplan 的规划需要经过设计工程师多次的设计迭代,从而获得一个互连线长尽量短、时序尽量收敛的 Floorplan 以供之后阶段进行自动布局布线。如今,采用 Mixed Placement 实现流程,Macro Cells 和 Standard Cells 通过由拥塞、互连线长和时序驱动的 Mixed Placer 引擎同时进行放置,与传统流程相比,Mixed Placement 可以大量减少设计工程师的手动工作量,从而实现更短的项目实现时间,并达到相当甚至更好的性能质量。而在最新的 Integrity 3D-IC 实现平台,Mixed Placement 功能可以完美继承到 3D-IC MoL 实现流程中,在进行 3D-IC Placement 的过程中帮助工程师用尽可能短的时间,获得满足要求的 Floorplan。3D-IC MoL Mixed Placement 引擎同样由时序驱动,同时摆放 Macro Cells 和 Standard Cells,同时如图中所示,还能支持在上层裸片中 80% 以上的高密度放置。

2. Pseudo-3D Timing Closure Flow

在完成初步的 3D-IC MoL Floorplan 之后,可以在 Integrity 3D-IC 平台中通过命令来建立 Pseudo-3D 时序收敛流程,完成 3D-IC MoL 的版图实现。主要分为 3D 层次化结构的重建、Bump 物理位置分配、Pseudo-3D 自动布局布线、以及 3D-IC 数据库的建立。

01. 重建 3D 层次化结构

相较于传统芯片的设计,3D-IC 设计的层次化结构的不同是显而易见的。3D-IC 设计由于会将芯片分为上下两个裸片—— Top Die 和 Bottom Die,天生就需要建立两个单元模块。工具会根据用户的设定,建立两个新的 Top-Level hInsts,随后将所有设计中的 Macro Cells 归入 Top hInst 中;剩下所有的 Standard Cells,在保留原有的层次化结构的基础上,全部归入Bottom hInst 中,其下级可继承保持原始设计中的所有层次化结构。

02. 分配 Bump 物理位置

从结构层面上实现三维分组之后,三维堆叠的互连问题也必须考虑。为了将上下裸片连接起来,最常用的方式是在顶部金属层上通过微米量级尺寸的 Micro Bump 实现上下层“面对面”(Face-to-Face)的堆叠连接,由此实现数据和电源电信号跨层传输。在 Pseudo-3D 流程中,所选用的 Bump Cells 的物理位置需要在做实际绕线之前就固定好,并记录其坐标信息。设计者不需要手动分配规划 Bump 的位置,Integrity 3D-IC 可以自动地将 Bump 逻辑连接关系插入跨层的时序路径中,并能根据设计师提供的 Floorplan 中单元的已有位置,同时在上下两个裸片上,智能地分配和优化 Bump Cells 的物理位置,做到高效的流程,自动的实现,智能的优化。

03. Pseudo-3D 自动布局布线

工作准备就绪后,我们就可以利用带有 Bump Cells 信息的 Pseudo-3D Floorplan 进行自动布局布线,Integrity 3D-IC 平台可以调用各种相应的传统二维布局布线引擎,完成 Placement、CTS、Routing 以及相应的设计优化。同时,Integrity 3D-IC 也可以支持跨层的时序路径的报告分析,支持显示例化单元 Instances 和路径所在的结构层级,帮助工程师完成静态时序分析。此外,Integrity 3D-IC 还支持跨层路径的并行时序优化,确保 3D-IC 设计的时序收敛。

04. 建立 3D-IC 数据库

最后一步,根据优化后的自动布局布线结果,建立 3D-IC 专用数据库——Hierarchical Database(HDB)。这个数据库中就包含了包括整个设计的工艺库信息,3D-IC 的堆叠信息,Bump 坐标信息,物理布局布线等设计信息等等。在通过Integrity 3D-IC 创建好用以明确 3D-IC 的堆叠对应信息的 Stacked Config 文件之后,需要将完成了布局布线的 pseudo-3D 数据库进行 Partition 拆分操作,将它按照上下裸片拆分成两个数据库,即 Top Die Database 和 Bottom Die Database。

将这两个完成 Partition 拆分的数据库以及 Stacked Config 文件读入 Integrity 3D-IC 中,合成创建 HDB 数据库。在 Integrity 3D-IC 平台中加载此数据库,就可以实现 3D-IC 设计的查看,包括可以实现在工具中上下两层 Floorplan 视图的切换,观察每层中的单元摆放、绕线等后端实现细节;也可以对包含三维堆叠信息的整体 3D Floorplan 视图进行直接查看;此外传统的时序调试器(Timing Debugger)也支持在 3D-IC HDB 中高亮跨层的时序路径,帮助工程师完成时序检查和设计调整,也可以进一步调用其他 Signoff 工具,完成后续签核工作。

存算一体和近存计算是解决 CPU / GPU / NPU 总线和大规模片上网络拥塞的有效手段。

通过 Integrity 3D-IC 特有的内存单元逻辑单元三维布局优化,芯片设计师可以更容易的实现高性能高带宽的系统设计,从而或者缩小原有系统封装面积或者进一步提高原有系统 PPA。