本文将阐述为何非隔离式DC-DC降压转换器(在本文中简称为降压转换器)在高输出电流下将高DC输入电压转换为很低的输出电压时会面临严峻挑战,并介绍可以实现高降压比,同时保持小尺寸的三种不同方法。

系统设计人员可能会面临以下挑战:在高输出电流下将高DC输入电压下变频为极低输出电压(例如在3.5 A时从60 V降至3.3 V),同时保持系统的高效率、小尺寸并实现简单设计。

将高输入-输出电压差值与高电流结合使用,会因为功耗过高自动将线性稳压器排除在外。因此,设计人员必须在这些条件下选择开关拓扑。但是,即使使用这种拓扑,对于空间有限的应用要实现足够紧凑的设计仍然相当困难。

DC-DC降压转换器面临的挑战

要实现高降压比,一种方案是使用降压转换器,因为它是将输入电压高效降至更低的输出电压(例如,VIN = 12 V降至VOUT = 3.3 V)、仍然具有大量电流,且保持小尺寸的一种拓扑选项。但是,在某些情况下,降压转换器要保持输出电压稳定,会面临严峻的挑战。为了理解这些挑战,我们需要记住,在连续导通模式(CCM)下工作的降压转换器的占空比(D)可简化为:

占空比和开关频率(fSW)的关系如下所示,其中导通时间(tON)是指在每次开关期间(T),控制FET保持开启的时长:

结合公式1和公式2可以看出,tON如何受降压比和fSW的影响:

从公式3可以看出,当输入-输出电压比(VIN⁄VOUT)和⁄或fSW增大时,导通时间会降低。这意味着降压转换器必须能够以很低的导通时间运行,以便在高VIN⁄VOUT比率下调节CCM中的输出电压,而在高fSW下这会更难实现。

我们假设在一个应用中,VIN(MAX) = 60 V,VOUT = 3.3 V,IOUT(MAX) = 3.5 A。在必要时,我们需要使用 LT8641 数据手册中的数值,因为在之后的章节中,我们将提供采用LT8641的解决方案。所需的最小导通时间(tON(MIN))对应最高输入电压(VIN(MAX))。为了评估这个tON(MIN),建议提高公式3的准确度。通过包含降压转换器的两个功率MOSFET的压降VSW(BOT)和VSW(TOP),并用VIN(MAX)替代VIN,我们得出:

通过在公式4中使用VIN(MAX)、fSW = 1 MHz,我们得出tON(MIN)为61 ns。为了计算VSW(BOT)和VSW(TOP),我们使用了LT8641数据手册中提供的RDS(ON)(BOT) 和RDS(ON)(TOP)值,且已知VSW(BOT) = RDS(ON)(BOT) × IOUT(MAX),VSW(TOP) = RDS(ON)(TOP) × IOUT(MAX)。从上述公式可得到61 ns的数值,这样短的时间数值,降压转换器很难保证tON(MIN);所以,系统设计人员不得不寻找可替代的拓扑。目前提供三种可实现高降压比的可行解决方案。

从上述公式可得到61 ns的数值,这样短的时间数值,降压转换器很难保证tON(MIN);所以,系统设计人员不得不寻找可替代的拓扑。目前提供三种可实现高降压比的可行解决方案。

三种紧凑型解决方案

解决方案1:使用LT3748非光耦反激式变压器

第一种选择是使用隔离拓扑,变压器具有N:1匝数比,负责执行大部分下变频。为此,ADI公司提供反激式控制器,例如LT3748,该控制器不需要第三个变压器绕组或光隔离器,使设计更简单,更紧凑。图1显示适用于这种情况的 LT3748 解决方案。

尽管与标准反激式设计相比,LT3748解决方案简化了设计并节省了空间,但仍然需要使用变压器。对于无需隔离输入端和输出端的应用,最好是避免使用该组件,相比非隔离解决方案,该组件会增加设计复杂性和增大尺寸。

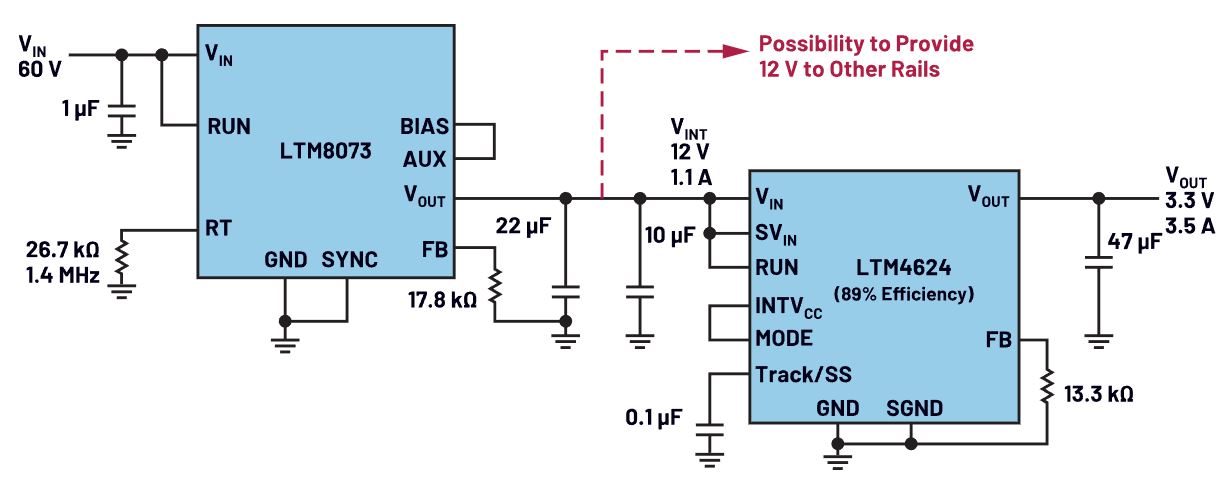

解决方案2:使用LTM8073和LTM4624 µModule器件

作为一种替代方案,设计人员可以通过两个步骤进行下变频。要实现更少的组件数量(仅为10个),可以使用2个µModule®器件和8个外部组件,如图2所示。此外,这两款µModule器件已集成各自的功率电感,为系统工程师免除了一项困难的设计任务。LTM8073 和 LTM4624 均采用BGA封装,尺寸分别为9 mm × 6.25 mm × 3.32 mm和6.25 mm × 6.25 mm × 5.01 mm (L × W × H),可提供小尺寸解决方案。

由于在这些条件下LTM4624展现的效率为89%,LTM8073最多为LTM4624的输入端提供1.1 A。由于LTM8073可以提供高达3 A输出电流,因此可用来为其他电源轨供电。为此,在图2中,我们选择12 V作为中间电压(VINT)。

尽管应避免使用变压器,但有些设计人员可能不愿使用需要两个独立的降压转换器的解决方案,尤其是无需采用中间电压为其他电源轨供电的情况下。

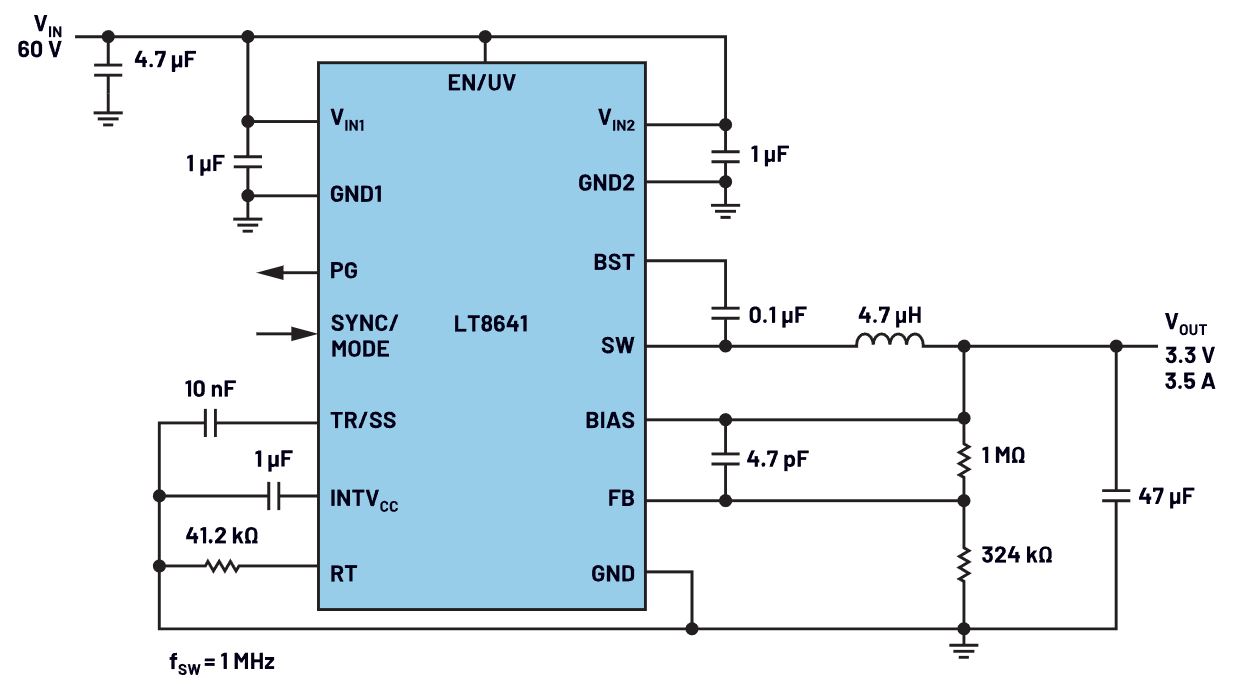

解决方案3:使用LT8641降压转换器

所以,在许多情况下,使用单个降压转换器成为首选,因为它是比较理想的解决方案,具有系统效率高、小尺寸和设计简单的特点。但是,我们前面不是展示降压转换器无法应对高VIN⁄VOUT和高fSW吗?

这个说法可能适用于大部分降压转换器,但并非全部。ADI产品系列中包含LT8641之类降压转换器,在整个工作温度范围内,它具有较短的最低导通时间,一般为35 ns(最大50 ns)。这些规格都在之前计算得出的61 ns最小导通时间以下,为我们提供了第3种可行的紧凑型解决方案。图3显示LT8641电路有多么简单。

还有一点值得注意,LT8641解决方案可能是3种解决方案中最高效的。事实上,如果与图3相比必须进一步优化效率,我们可以降低fSW并选择更大的电感尺寸。

尽管也可以通过解决方案2来降低fSW,但集成功率电感后无法灵活提高效率,达到高于某个点的目标。此外,使用两个连续下变频级对效率的负面影响较小。

在使用解决方案1时,由于在边界模式下运行,以及在非光学反馈设计中移除了所有组件,因此反激式设计的效率非常高。但是,效率不能完全优化,因为可选的变压器数量有限,而解决方案3则有广泛的电感产品系列可供选择。

图 1. 采用 LT3748 的电路解决方案,将 60 V 输入下变频至 3.3 V 输出。

图 2. 采用 LTM8073 和 LTM4624 的电路解决方案,将 60 V 输入下变频至3.3 V 输出。

图 3. 采用 LT8641 的电路解决方案,将 60 V 输入下变频至 3.3 V 输出。

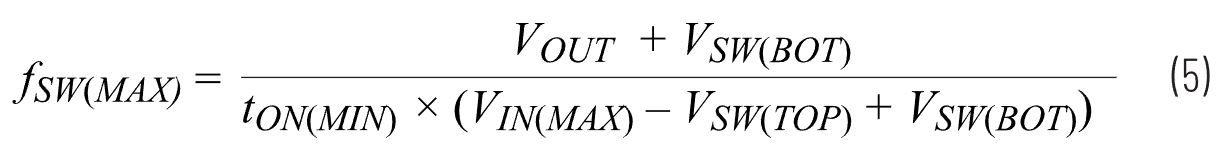

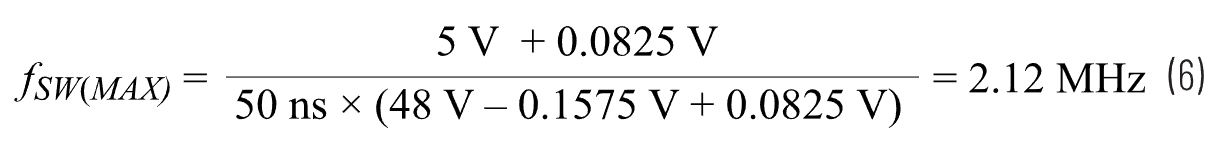

检查LT8641是否满足要求的另一种方法

在大多数应用中,公式4中唯一可调的参数是开关频率。因此,我们重新变换公式4,以评估LT8641在给定条件下允许的最大fSW。于是,我们得到公式5,LT8641数据手册的第16页也提供了这个公式。

我们在以下示例中使用此公式:VIN = 48 V,VOUT = 3.3 V,IOUT(MAX) = 1.5 A, fSW = 2 MHz。汽车和工业应用中经常使用48 V输入电压。在公式5中代入这些条件后,我们得出:

因此,在给定的应用条件下,在fSW高达2.12 MHz时,LT8641能够安全运行,证实LT8641是适合此应用的一个不错的选择。

结论

本文提出了三种不同的方法,以在高降压比下实现紧凑型设计。LT3748反激式解决方案不需要使用笨重的光隔离器,推荐用于需要隔离输入端和输出端的设计。第2种方法需要使用LTM8073和LTM4624 µModule器件,当设计人员为应用选择最佳电感犹豫不决,以及⁄或何时必须提供额外的中间电源轨时,这种解决方案会非常有用。第3种方法基于LT8641降压转换器进行设计,如果只是要求实现陡电压下变频时,可提供紧凑且简单的解决方案。

文章来源:亚德诺半导体