作者:蒋修国

在进行比较复杂的板子设计的时候,你必须进行一些设计权衡。因为这些权衡,那么就存在一些因素会影响到PCB的电源分配网络的设计。

当电容安装在PCB板上时,就会存在一个额外的回路电感,这个电感就与电容的安装有关系。回路电感值的大小是依赖于设计的。回路电感的大小取决于电容到过孔的这段线的线宽和线长,走线的长度即连接电容和电源/地平面长度,两个孔间的距离,孔的直径,电容的焊盘,等等。如图1所示为各种电容的安装图形。

图1 最佳的和最差的电容布局

减小电容回路电感的设计要点:

■孔要放在离电容尽可能近的地方。减小电源/地的孔间距。如果可以,用多对电源/地孔并联在一起。诸如电流极性相反的两个孔放置的尽量近,电流极性相同的孔放置的尽量远。

■用短而宽的走线来连接孔和电容引脚。

■把电容摆放在PCB的表面(顶层和底层)尽量靠近他们相应的电源/地平面。这样能减小孔之间的距离。在电源/地之间用薄的电解质。

接下来是三种不同情况的设计,对于电容的安装和传播电感。图2表示的是各种设计情况对回路电感量的引入情况。

图2 设计情况

情况1-差的设计

■设计人员不关注电源分配网络(PDN)的设计。

■孔的间距没有优化。

■电源和地平面间的距离没有优化。

■孔到电容引脚之间的走线距离较长。

对于整个回路电感大小来讲,回路电感主要来自所布的线,因为与其它两种情况比较,差的设计时的线长是它们(好的设计和非常好的设计)的5倍。从安装电容的底层到最近平面的距离也是回路电感大小的主要因素。因为这是没有优化的(10mil),走线对整个回路电感大小的影响是非常大的。同样,因为设计人员在电源和地之间用了10mil的电介质材料,那么回路电感的次要因素来自传播电感。过孔间的距离没有优化的效果相对于小孔的长度就没有那么的显著。孔的影响在比较长的过孔时会变得更大。

情况2-好的设计

■设计人员关注了部分电源分配网络(PDN)的设计。

■孔的间距有所改善。孔的长度保持不变。

■电源和地平面间的距离有所改善。

■过孔到电容引脚之间的走线距离经过了优化。

走线的回路电感依然还是整个回路电感的主要贡献者。但是,好的设计的走线回路电感要比差的设计情况的的走线回路电感小2.7倍左右。因为设计人员减小了电介质的厚度,从10mil减小到了5mil,传播电感减小了一半。由于减小了过孔间的距离,过孔的影响有了一点点改善。

情况3-非常好的设计

■设计人员非常注重PDN的设计。

■孔的间距和长度都有改善。

■电源和地之间的距离也进行了充分的优化。

■ 过孔到电容引脚之间的走线距离经过了优化。

非常好的设计的走线的电感比差的设计的走线电感要小大约7.65倍。由于减少了走线长度,在PCB板上减少了从电容安装的底层表面到最近的平面层的厚度,这就达到了目的。由于设计人员已经优化了电源和地之间的电解质层厚度,传播电感就会大大的减小。由于孔间距和孔长度大大的减小,那么过孔的回路电感也得到了显著改善。相比差的设计,由于7个主要因素的其中之一减少,非常好的设计情况的总回路电感就被减少了。.

在PCB板上,额外的过孔回路电感通过安装电容被引入,这样就降低电容的谐振频率。当你在设计电源分配网络(PDN)时,必须要考虑到这个因素。在高频设计的时候,减小回路电感是降低阻抗的唯一能看得见的方法。

对于给定的电源,相比较非常好的设计和差的设计情况,PDN工具产生的报告显示非常好的设计的PCB截止频率会更高。这也许与预期的结果是相反的,因为相对于对低截止频率的去耦,对较高截止频率的去耦需要更多的电容。

对于非常好的设计的情况,较高的截止频率意味着能对较高频率进行去耦。摆放在PCB板上的电容对噪声直到一个较高频都有去耦效果。

对于差的设计,对超过较低截止频率的PCB板不能去耦。任何额外的电容增加,即增加超过截止频率的去耦电容只能增加BOM成本而对去耦效果没有任何影响。相对于非常好的设计,对于差的这种设计情况,其电源分配网络的设计对于某一特定频率的噪声更容易受到影响

作为另外一个例子,假设一块20层的PCB板总共有115mil的厚度。电源层在第3层。从第一层(FPGA在的这一层)到第3层的厚度有12mil。那么从底层到第3层的厚度就是103mil。电源和地层被3mil后的电介质分离开。对于这种轨迹的BGA孔的电感大小为5nH(对于这种电源轨迹5对孔)。为了应对第一层比较紧密的布局布线区域,与之相关联的去耦电容都安装在底层。由于这样安装会有很长的过孔,这种权衡设计导致了很高的电容安装电感值。经过充分优化后,0402封装的电容在底层的安装电感是2.3nH,而同样的电容放在第一层的安装电感是0.57nH。

为了改善这种给轨迹的PDN效果,你可以把一些高频电容放置在第一层,同时把中频和bulk电容还是放在原来的位置上即底层。这种电路设计对PDN是截止的解决方法,因为高频电容是在截止频率以下作为第一响应的电容。电容的效果依赖于总的回路电感(电容的安装电感+传播电感+BGA孔的电感)与FPGA。你可以把高频电容放在第一层并离FPGA稍微远一点点的地方。电容放在FPGA breakout区域外的传播电感是0.2nH。相对于原来放置在底层的方法,这种新的放置方法还是有益的,因为总的回路电感(0.57nH+0.2nH+0.05nH=0.82nH)比放置在底层的时候的总电感要小。

PCB板的传播电感是与设计是相关,电源和地平面间的介质中它是均匀存在的。3mil厚度或者更薄的厚度是最佳的减小平面传播电感的设计。你可以根据如下的设计指导来提升PDN的性能。

如下的是关于顺序重要性的设计指导,从第一层到底层—在第一层的设计指导是最重要的。

■减小电源和地层间电介质厚度。当设计板子的叠层时,确定电源、层和其他的层。举一个例子,如叠层PWR1 - GND1 - SIG1 - SIG2- GND2 - PWR2要优于PWR1 - SIG1 - GND1 - SIG2 - GND2 - PWR2这种叠层。第二种情况的结果是没有对电源和地之间的距离优化的设计。这样的设置会导致大电容传播电感在PWR1/GND1之间比在PWR2/GND2之间的电感大。你可以在电源和地平面之间找到一种典型的3mil的电介质厚度而不增加额外的成本。对于额外的性能改善,考虑比3mil更薄的电介质厚度。但是,这会导致PCB的成本上升。

■当选定电容的时候,选择多个电容值,而不是选择一个相同值的大电容来达到目标阻抗。在PDN中,阻抗的峰值是由谐振反应形成的。高ESR在谐振频率点能抑制谐振,因此减少阻抗峰值的高度。在电容的谐振频率处和阻抗峰值处,用一些电容值相同的电容能截止的减少ESR。

在一个很宽的频率范围内,选择多种电容值的电容种类,能维持一个相对高的ESR。

■选择放置高频电容的位置,以减少整个回路电感。整个电感是由电容的ESL、安装电感、传播电感和BGA的过孔电感组成的。在放置电容时优先放置高频电容,其次是中频和低频电容。

■当在分割平面时,确保平面的形状成适当的方形。避免狭长的平面形状,因为这样做会限制电流的大小和增加平面的传播电感。

■中频和低频的电容对于如何放置没有那么的敏感。可以把他们放在离FPGA稍微远一点的地方。

权衡多路设计的情况

在一块有多路外设的PCB板上,你的设计就不能再共享一个供电电源。这也许需要你通过你的设计去执行DDR的电源接口,联合各种I/O口的电源轨迹,或者联合各种接收端的电源轨迹以减少PCB的BOM成本和PCB的布局复杂度。

电源轨迹共享增加了PDN的复杂度,同时在PCB上和die的位置处也增加了大量的噪声。对于多路的情况,设计电源的分配解决方法主要有两步:

1 低频解决方法

2 高频解决方法

在非常低频的时候,第一步确保VRM的大小是否适合处理各种电流的需要。

低频去耦一定要考虑清楚各种组合电源供电电流的情况。Bulk电容一定要选择能覆盖目标阻抗所覆盖的频段。做到精确的知道频率范围是有困难的,因为这有一个区域超过了阻抗曲线,这是在die上给定的电源区域,建立在自己的最大电流消耗上,而不是与其它路电流相关联的由同一个供电电源供电组合的电流消耗。对于设计,bulk电容去耦的频率范围估计是从DC到大约5~10MHz。

在共享多路电源的时候,通过PDN工具按照相似的方法使用这种设计方法,但是推荐你在最高的截止频率点去耦。对于单一和共享多路电源的去耦,这是成功实现单一PDN方法设计的流程。这种方法是合适于与电源路之间与相似电流要求的电源路设计的。但是,对于这种方法这有几个例外。

这个例子是电源共享在核心电源供电(Vcc)和PCI Express hard IP Block(VccHIP)电源供电。例外的原因是:

■VCC的电流会比VCCHIP的大很多。

■对比VCC和VCCHIP,VCC的BGA的过孔电感会比VCCHIP低很多。

■对比VCC和VCCHIP,VCC的截止频率会比VCCHIP低很多。

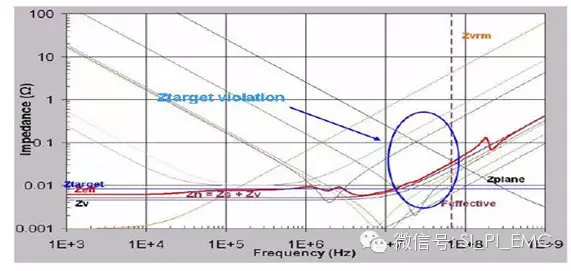

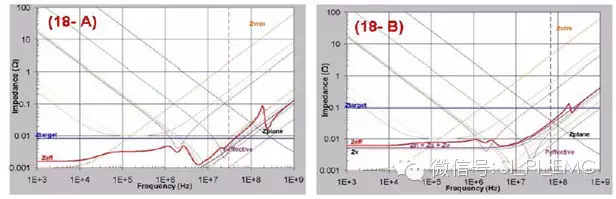

因此,对于电源设计情况,在BGA过孔处使用最高截止频率去耦是不适用的。如图3所示的是VCC、VCCHIP电源路组合阻抗曲线不符合目标阻抗的情况,相当于不符合VCCHIP的截止频率去耦。这是因为去耦电容效果被限制了

图3 VCCHIP的截止频率阻抗曲线

按照以前的解释,高频的噪声在电源轨迹中,主要是由于自己的瞬态电流产生的。对于共享电路最高截止频率的去耦设计指导书是基于整个瞬态电流的阻抗计算,这是“过设计”的要求。

图4 更改电源路的共享情况

在这种情况下,你必须基于PCB去耦项目用整个瞬态电流来计算目标阻抗曲线,相当于电源路截止频率的最大的电流消耗。在VCC和VCCHIP电源路共享的例子中,你必须用VCC电源路的截止频率。如图3-A所示为核心电源去耦的截止频率的组合电源路的阻抗曲线。对于核心电源,用沿着BGA的球或者过孔的(VCC+VCCHIP)的总电流得到阻抗曲线。那么你可以检查核对结果是否符合单个电源设计指导的目标阻抗。

基于同样的去耦项目如图4-A一样,如图4-B所示为VCCHIP电源的阻抗曲线。但是,当得到这条曲线时,只有对于VCCHIP需要考虑电流消耗和BGA过孔数。如图4-B所示,直到VCCHIP电源的截止频率,VCCHIP的阻抗曲线都达到了目标阻抗。

最终的去耦项目必须达到各自目标阻抗的频率。如果存在一些特殊的违反设计目标的情况,可以尽量小的调整以优化去耦项目。

遇到类似的情况,可以根据VCC和VCCHIP的例子对任何供电电源组合进行优化。

在一块PCB板上,当有多个FPGA需要从同一个电源供电时,你可以使用相似的方法来应对这种情况。对于设计低频解决方案一定要用芯片的总电流消耗,对于高频解决方案设计,一定要用其中一个芯片的电流消耗。你可以使用同样数目的电容给其他芯片在高频情况时去耦。

当与场分析工具得到的解决方案相比较,如果两个FPGA芯片之间的空间比较小,高频方可能导致轻度的过设计,因为场分析工具是考虑了板子的布局情况的。这可能是因为芯片之间比较接近,几乎没有电容能够截止地满足两个芯片的位置的要求。这也取决于从FPGA芯片端看到的电容的截止回路电感。

一个常用的设计权衡是建立一个独立的电源平面,和从一个供电电源给不同的电源网路供电,使用滤波器来供给干净的电源给电源网路。大多数情况下滤波器是磁珠,连接在板子上的两个电源之间。作为规则是,你可以按照如下设计指导,给一个电源网络提供干净的电源。

■当磁珠连着两个电源网络的时候,确保安装电感是最小的。

■根据如下所列的特性选择磁珠,确保电源电路的电流消耗要小于磁珠的额定电流。

■封装尺寸(0603,0402等等)

■额定电流

■直流电阻

■在目标频率的阻抗(10 MHz, 100 MHz, 1 GHz等等)

■磁珠的等效的RLC模型频率响应一定尽量与datasheet中给定的相符合。

■做交流分析时,在所覆盖的频率内,一定要包含磁珠的模型,还有各种为了达到目标阻抗而选用的电容。当设计电容的等效RLC模型的时候,安装电感要作为模型的一个组成部分考虑进去,如果交流分析没有峰值出现在我们感兴趣的频段(DC to 200 MHz),你就可以使用磁珠隔离来提供干净的电源。

■通过上面仿真得到的PDN的结果一定能达到我们感兴趣的频段内目标阻抗的要求。

本文转载自:硬件十万个为什么