摘要

随着传统DRAM器件的持续缩小,较小尺寸下寄生电容的增加可能会对器件性能产生负面影响,未来可能需要新的DRAM结构来降低总电容,并使器件发挥出合格的性能。本研究比较了6F2蜂窝动态随机存取存储器 (DRAM) 器件与4F2垂直通道访问晶体管 (VCAT) DRAM结构的寄生电容。结果表明,与6F2结构相比,4F2结构显著降低了节点接触 (NC) 与位线 (BL) 之间的寄生电容。尽管4F2器件其他组件之间的寄生电容相比6F2器件略有增加,但它们仍处于支持器件达成目标性能的合格水平。相比6F2器件,4F2 DRAM器件的总寄生电容得到有效降低,可能在器件尺寸较小的情况下提供更优的性能。

简介

随着传统6F2 DRAM器件的不断缩小,位线与接触节点 (CBL-NC) 之间的寄生电容由于这些DRAM组件之间距离的减少而增加。这种电容的增加导致位线感应裕量和刷新时间下降,进而对存储器性能产生负面影响。用于下一代DRAM器件的4F2 VCAT DRAM架构就是为了解决这一问题并显著降低寄生电容。

评估新的DRAM架构通常会采用基于硅晶圆的实验,但这种方法既耗时又昂贵。在本研究中,我们使用SEMulator3D®的虚拟工艺建模来评估6F2和4F2 DRAM器件之间的寄生电容,对比了不同DRAM结构中存在的各种寄生电容,并评估了4F2 DRAM器件相比6F2 DRAM器件在总电容方面可能实现的改进。

器件结构和仿真方法

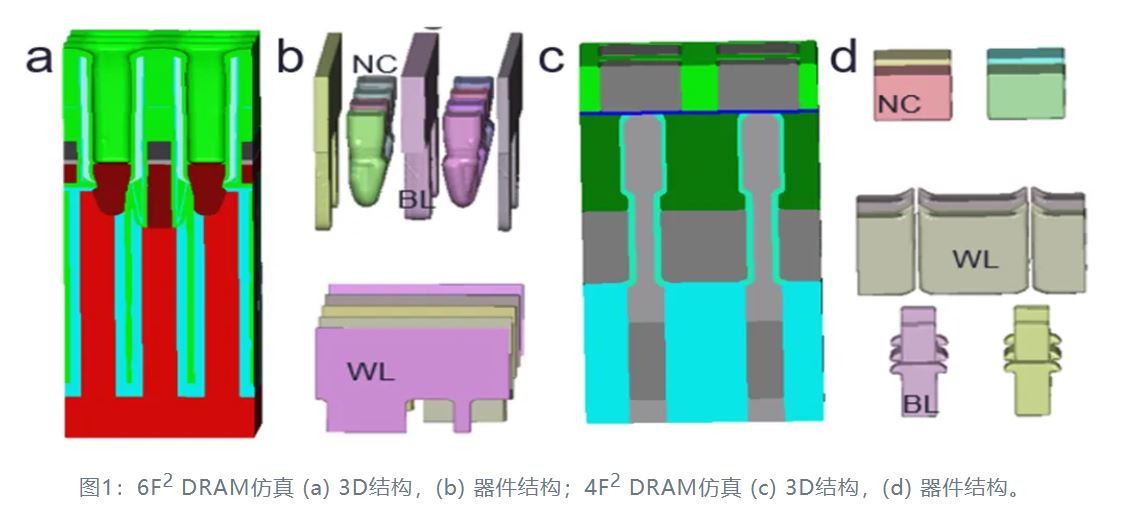

本研究使用版图数据和工艺步骤数据组合在工艺建模平台中构建虚拟3D结构。图1a和图1b分别展示了6F2 DRAM器件的仿真3D结构及其器件结构,图1c和图1d分别展示了4F2 DRAM器件的仿真3D结构及其器件结构。我们对这些结构进行了电容提取,以计算每个DRAM器件中的寄生电容。

器件仿真结果

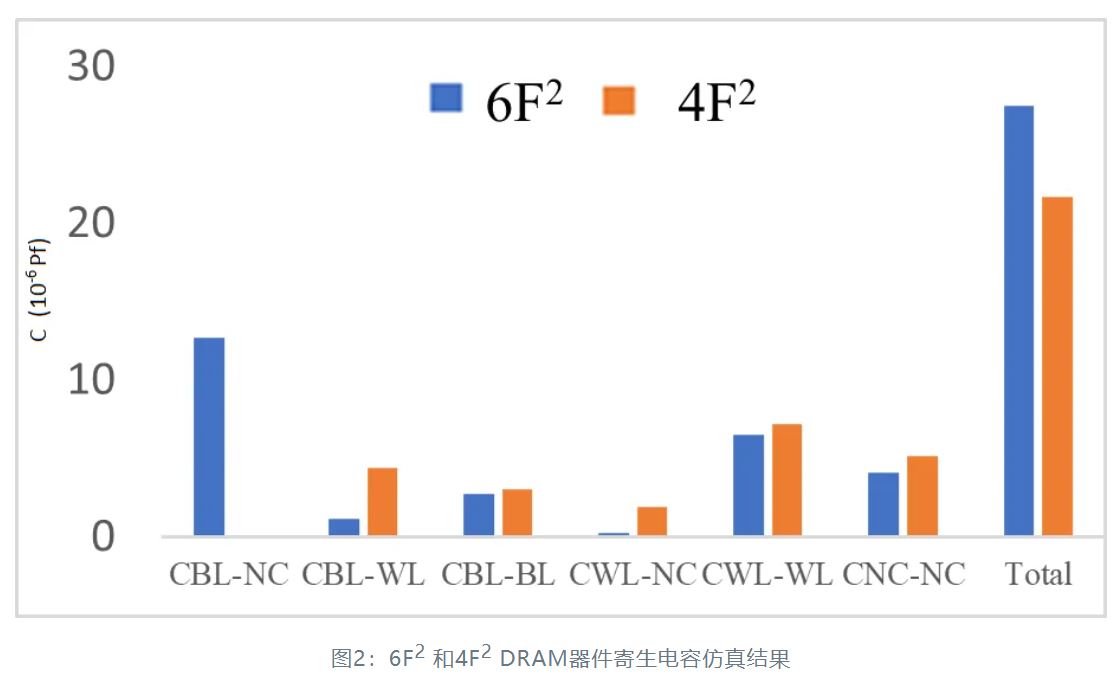

图2显示了6F2 和4F2 DRAM器件的寄生电容仿真结果。在4F2 DRAM结构中,CBL-NC显著减少,主要原因是与6F2 DRAM相比,位线与接触节点之间的间距较大。由于字线未被埋入且比在6F2 DRAM中更接近位线,CBL-WL和CWL-NC在4F2 DRAM中更大。由于4F2和6F2 DRAM器件的位线结构差异不大,CBL-BL相当。由于4F2 DRAM中的关键尺寸更大且间距更小,CWL-WL和CNC-NC表现较差。总体而言,与6F2结构相比,4F2结构的总寄生电容仍显著减少。

与6F2 DRAM器件相比,4F2 DRAM器件的性能有所提升。与6F2结构相比,4F2结构中的CBL-NC以及总电容得到了有效降低(见图2)。

使用4F2结构时,某些子元件的寄生电容会增加,但这些电容值远远低于6F2结构中的CBL-NC ,从而降低了总电容,这意味着在工艺上有足够的窗口来实现合格的器件性能。尽管CBL-NC得到了大幅减少,但在4F2 DRAM中,CWL-WL仍然是最大的寄生电容元件。然而,字线间的电容会影响晶体管栅极的控制,因此在4F2 DRAM设计中可能需要更加关注器件控制。

结论

我们使用虚拟工艺建模来研究不同DRAM结构的电容。结果表明,与6F2 DRAM结构相比,由于4F2 DRAM器件中主要寄生电容 (CBL-NC) 的减少,4F2 DRAM结构的总寄生电容可以显著降低。特别是在器件尺寸缩小的情况下,4F2 DRAM结构可能比6F2器件提供更好的性能。

参考资料:

[1] Q. Wang, Y. De Chen, J. Huang, B. Vincent and J. Ervin. 2022 China Semiconductor Technology International Conference (CSTIC)2022, pp. 1-4.

文章来源:泛林集团