省时省力地优化差分换层过孔

judy-- 周四, 05/23/2024 - 10:38

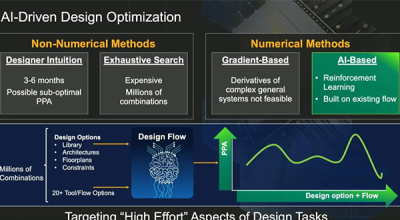

对 SoC 设计人员来说,利用众多仿真参数优化设计是一项极具挑战性的工作,因为这需要大量的计算资源、时间和成本。

对 SoC 设计人员来说,利用众多仿真参数优化设计是一项极具挑战性的工作,因为这需要大量的计算资源、时间和成本。

要想确保集成电路的可靠性,有必要了解封装的热特性。要将器件结温保持在允许的最大限值以下,集成电路必须能够通过封装有效散热

本文将通过一个简单的测试案例,展示如何使用 Cadence Clarity 3D Solver 和 Optimality Explorer 省时省力地优化差分对过孔过渡。

系统设计领域充满变数,确保信号完好无损地到达目的地还只是冰山一角。随着封装密度不断提高、PCB 线路不断细化以及频率不断飙升

在设计传输线时必须考虑到 RF 反射。传输线设计的基本原则之一是确保驱动端、走线和负载端的特性阻抗相匹配。

先进电子产品的仿真驱动型设计涉及哪些流程?电子产品的复杂程度远远超过电路,这意味着必须在多个层面上进行仿真驱动的设计

作为电源完整性设计的一部分,电感对于总阻抗的影响十分重要,值得关注。

每个电子设计人员对电容器都不陌生。电容器由两块导电板组成,中间隔着一层电介质

本文将举例介绍不同类型的谐波失真,以及产生的原因。

全新的 112G-ELR SerDes IP 可以支持 45dB 插入损耗,拥有卓越的功耗、性能、面积(PPA)指标,是超大规模 ASICs,人工智能/机器学习(AI/ML)加速器